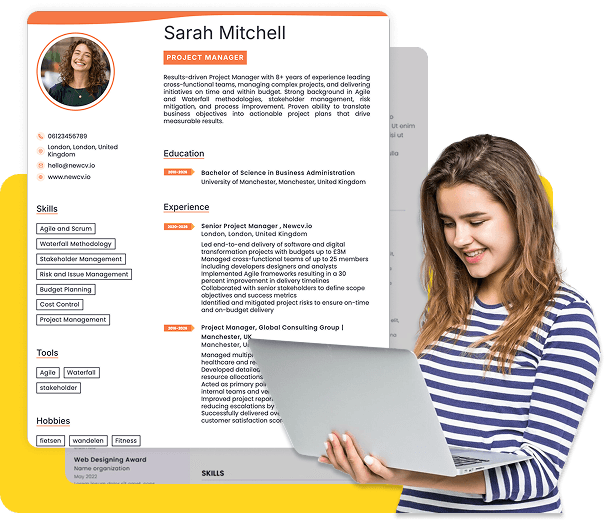

Choose from a wide range of NEWCV resume templates and customize your NEWCV design with a single click.

Use ATS-optimised Resume and resume templates that pass applicant tracking systems. Our Resume builder helps recruiters read, scan, and shortlist your Resume faster.

Use professional field-tested resume templates that follow the exact Resume rules employers look for.

Create Resume

Use professional field-tested resume templates that follow the exact Resume rules employers look for.

Create ResumeVerification Engineer resumes are evaluated through an extremely technical screening pipeline. Recruiters and ATS systems do not simply check whether a candidate has “verification experience.” They search for structured evidence of verification methodology expertise, simulation environments, hardware validation workflows, and deep familiarity with modern verification frameworks.

In semiconductor companies, chip design firms, FPGA teams, and SoC development environments, Verification Engineers are responsible for ensuring design correctness before fabrication or production release. This means resumes must clearly communicate experience with verification architectures, simulation tools, coverage strategies, and debugging methodologies.

A generic engineering resume does not perform well for this role. An ATS-friendly Verification Engineer resume template must mirror how verification professionals are evaluated inside chip design hiring pipelines.

This guide explains the recruiter evaluation logic and provides a fully optimized ATS-friendly resume template specifically structured for Verification Engineer roles.

Verification Engineer roles are highly technical. ATS systems used by semiconductor companies typically scan resumes for verification ecosystem signals rather than general engineering experience.

The system attempts to classify candidates based on three verification capability clusters.

Verification teams expect candidates to understand structured methodologies such as UVM or SystemVerilog-based verification frameworks.

ATS systems frequently search for:

SystemVerilog

UVM (Universal Verification Methodology)

OVM / VMM

Constrained random verification

Functional coverage

Even candidates with strong chip design experience often fail ATS screening due to structural problems in their resumes.

The most common failure pattern is vague engineering language.

Weak Example

Worked on verifying hardware modules and supporting design teams.

Good Example

Developed SystemVerilog-based UVM testbenches to verify AXI bus protocol compliance across multi-core SoC modules.

Explanation

The strong example exposes verification methodology, architecture context, and protocol validation responsibilities.

ATS systems rely heavily on these signals to classify verification expertise.

Verification Engineer resumes perform best when they present technical verification signals early in the document.

Recruiters reviewing semiconductor resumes typically scan for verification frameworks within the first few seconds.

Professional Summary

Verification Methodologies

Simulation & Verification Tools

Verification Engineering Experience

Architecture & Protocol Knowledge

Education / Technical Certifications

This structure allows ATS systems to extract verification-specific signals before scanning work experience details.

Assertion-based verification

If these signals are absent, the candidate may be classified as a design engineer rather than a verification engineer, which removes them from verification-specific searches.

Verification engineers spend significant time in simulation environments diagnosing design behavior.

Recruiters often filter resumes for:

ModelSim

VCS

QuestaSim

Cadence Xcelium

Synopsys tools

Waveform debugging

Resumes that clearly reference simulation tools and debugging workflows rank significantly higher in ATS queries.

Verification engineers must understand the design they are validating.

ATS systems often look for architecture keywords such as:

SoC verification

FPGA validation

Bus protocols (AXI, AHB, PCIe)

Cache coherence

Memory controllers

Without architecture context, resumes may appear too generic to represent real verification engineering experience.

The following resume example reflects the structure commonly used by engineers hired into high-level verification roles at semiconductor and hardware companies.

Candidate Name: Jonathan Mitchell

Location: San Jose, California

Job Title: Verification Engineer

PROFESSIONAL SUMMARY

Verification Engineer with 8+ years of experience validating complex SoC architectures using SystemVerilog and UVM-based verification environments. Skilled in developing scalable verification frameworks, implementing constrained random testing strategies, and performing functional coverage analysis to ensure design correctness. Experienced in verifying high-performance chip components including memory controllers, bus protocols, and multi-core processing modules.

VERIFICATION METHODOLOGIES

Universal Verification Methodology (UVM)

SystemVerilog Testbench Development

Constrained Random Verification

Functional Coverage Analysis

Assertion-Based Verification

Directed and Randomized Testing

SIMULATION & VERIFICATION TOOLS

Synopsys VCS

Cadence Xcelium

Mentor QuestaSim

Verdi Debugger

ModelSim

Git Version Control

PROFESSIONAL EXPERIENCE

Senior Verification Engineer

QuantumChip Technologies – San Jose, California

2020 – Present

Responsible for functional verification of high-performance SoC components used in enterprise networking processors.

Designed and implemented UVM-based verification environments for validating AXI bus protocol interactions across multiple processing modules.

Developed constrained random test scenarios to improve verification coverage across complex memory controller subsystems.

Performed waveform analysis using Verdi to debug timing violations and protocol mismatches.

Implemented SystemVerilog assertions to detect bus transaction violations during simulation cycles.

Conducted functional coverage analysis to ensure verification completeness before design sign-off.

Collaborated with RTL designers to diagnose and resolve architectural defects discovered during simulation.

Verification Engineer

SiliconCore Microsystems – Austin, Texas

2017 – 2020

Supported verification of FPGA-based networking processors used in high-speed data communication systems.

Built SystemVerilog testbenches to validate packet processing pipelines and network interface modules.

Verified PCIe and Ethernet protocol interactions within FPGA subsystems.

Developed regression test suites to validate firmware and hardware integration.

Investigated simulation failures through waveform debugging and log analysis.

Assisted design teams in resolving functional defects discovered during verification cycles.

VERIFICATION PROJECT HIGHLIGHTS

Achieved 98% functional coverage across a multi-core SoC subsystem using constrained random testing techniques.

Identified a critical AXI bus arbitration defect prior to tape-out through simulation debugging.

Designed automated regression testing frameworks to validate FPGA module updates.

ARCHITECTURE & PROTOCOL KNOWLEDGE

AXI / AHB Bus Protocols

PCI Express

Ethernet Networking Interfaces

Memory Controller Architectures

Multi-Core SoC Designs

EDUCATION

Bachelor of Science – Electrical Engineering

University of California, San Diego

The template performs well because it aligns with how semiconductor recruiters search for verification engineers in ATS databases.

Recruiters often build queries such as:

“Verification Engineer + UVM”

“SystemVerilog Verification Engineer”

“SoC Verification + AXI”

This resume structure surfaces those signals immediately through dedicated methodology and tool sections.

It also avoids common ATS parsing problems such as:

Hiding tools inside paragraphs

Omitting verification frameworks

Using vague engineering language

When screening resumes, verification hiring managers look for evidence that the candidate understands how to build and execute verification environments.

Three indicators stand out strongly.

Candidates who design verification environments appear significantly more senior than those who only run simulations.

Experience validating industry protocols such as AXI or PCIe signals real hardware architecture knowledge.

Verification engineers who reference functional coverage targets and verification completeness show maturity in the verification process.

Verification resumes frequently fail because they describe activities rather than technical methodology.

Weak Example

Verified chip modules and worked with design engineers to resolve issues.

Good Example

Developed SystemVerilog UVM testbench components to validate memory controller logic and identify transaction protocol violations during simulation.

Explanation

The strong example clearly demonstrates verification framework usage, architecture context, and debugging responsibility.

Recruiters interpret this as a candidate capable of owning verification infrastructure.

ATS systems rank resumes higher when verification-related keywords appear across multiple sections rather than a single list.

High-performing resumes usually distribute signals across three areas.

UVM

SystemVerilog

Constrained random testing

Functional coverage

VCS

QuestaSim

Xcelium

ModelSim

SoC verification

FPGA validation

Bus protocols

This keyword distribution helps ATS systems correctly classify the candidate as a verification specialist rather than a general hardware engineer.

Modern verification teams are increasingly responsible for validating extremely complex chip architectures, particularly in AI accelerators, networking processors, and high-performance computing systems.

As a result, recruiters now prioritize candidates who demonstrate:

Advanced verification methodology expertise

Deep protocol validation experience

Strong debugging and simulation analysis skills

Collaboration with RTL design teams

Resumes that reflect methodology ownership and architectural awareness stand out significantly during screening.